开发专栏

NEW

最近的电子机械常使用通过机械内部或连接器向外部通信,以此来完成GB级的高速数据传送。

例如PC就是通过USB、HDMI、Display Port、PCI express、SATA等串联的高速差动接口(以下简称I/F),来完成高带宽的数据和高精度图像的传送。

此外,民生设备的数字TV面板以及产业机械的机器视觉摄像电缆I/F、办公用打印机的扫描仪等设备上也广泛采用LVDS和V-by-One® HS这样高速串联传送技术。

这些高速传送在物理层上的差动方式采用被称为LVDS(Low Voltage Deferential Signaling)或CML(Current Mode Logic)的技术。

差动的物理层为何会高速?

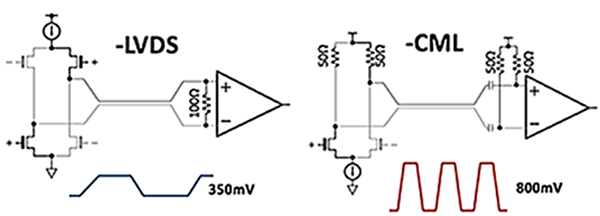

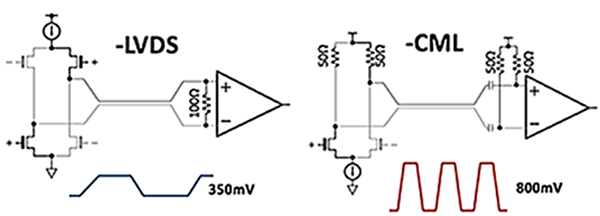

高速串联传送上使用的LVDS和CML采用图1这样的差动I/F。

在差动的高速传送上、电流从驱动器的稳定电流源回路向传送回路流动,用数百mV左右的小振幅来传送数据。

小振幅可缩短信号从低到到高;从高到低的变化时间,容易增加单位时间内传送的Bit数。还可以控制消耗电流和发热,降低不必要的辐射噪音。

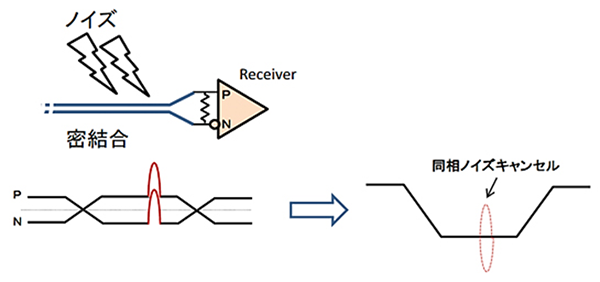

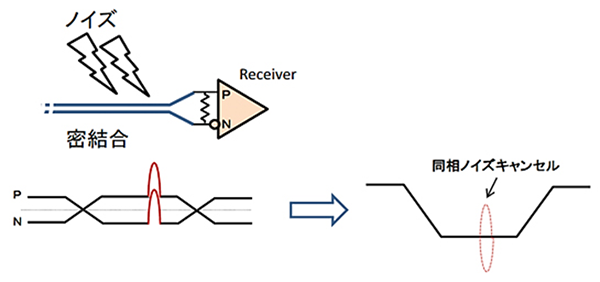

另一方面,振幅小则噪音容限减少。使用差动传送方式,理论上可以在接收端的差动回路上像图2那样消除共模部分(即噪音)。

差动传送方式还能通过差动间的信号结合来消除放射到外部的电磁界,控制不必要的辐射(EMI)和与其相接的Line或回路的交调失真。

在差动的高速传送上、电流从驱动器的稳定电流源回路向传送回路流动,用数百mV左右的小振幅来传送数据。

图1 LVDS与CML差动驱动等价回路

小振幅可缩短信号从低到到高;从高到低的变化时间,容易增加单位时间内传送的Bit数。还可以控制消耗电流和发热,降低不必要的辐射噪音。

另一方面,振幅小则噪音容限减少。使用差动传送方式,理论上可以在接收端的差动回路上像图2那样消除共模部分(即噪音)。

图2 差动接收器 消除共模噪音

差动传送方式还能通过差动间的信号结合来消除放射到外部的电磁界,控制不必要的辐射(EMI)和与其相接的Line或回路的交调失真。

产品与SerDes的动作

Serializer・De-Serializer(SerDes)是应用了这一物理层的代表性的半导体。

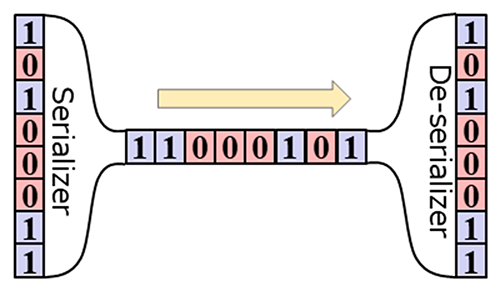

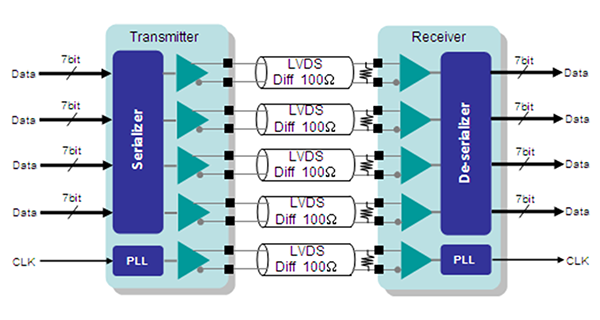

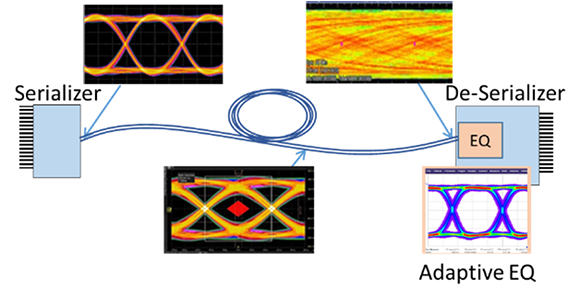

就像图3那样,Serializer能将从左方输入的并联总线的信号串联化。然后De-Serializer又能将接收到的串联信号转回成并联。

就这样SerDes能将大Bit的总线信号串联化,使用更少的信号线,作为总线信号的假想线缆来动作。

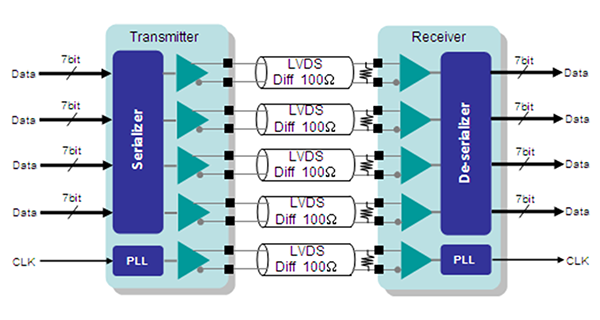

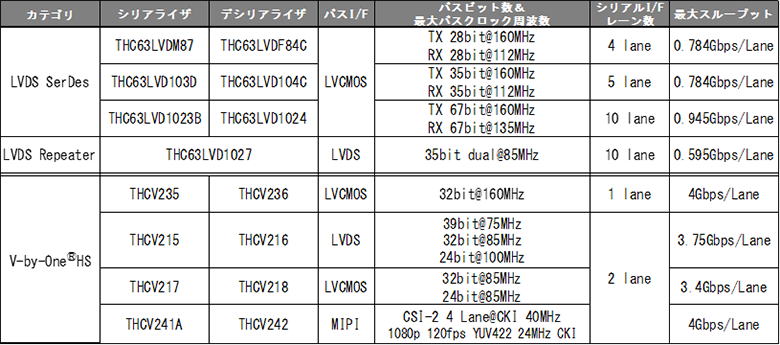

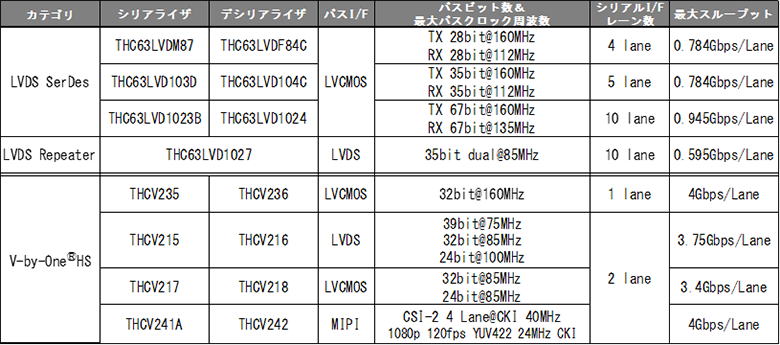

THine Electronics发布了应用LVDS、CML物理层的各种SerDes产品。表1是LVDS SerDes与CML物理层的V-by-OneⓇ HS的产品案例。

有总线Bit数为LVDS SerDes 28,35,70Bit;V-by-OneⓇ HS 24,32,39Bit等的产品,可根据必要的总线宽幅和同期时钟的周波数来选择产品。

就像图3那样,Serializer能将从左方输入的并联总线的信号串联化。然后De-Serializer又能将接收到的串联信号转回成并联。

就这样SerDes能将大Bit的总线信号串联化,使用更少的信号线,作为总线信号的假想线缆来动作。

图3 Serializer与De-Serializer的动作

THine Electronics发布了应用LVDS、CML物理层的各种SerDes产品。表1是LVDS SerDes与CML物理层的V-by-OneⓇ HS的产品案例。

有总线Bit数为LVDS SerDes 28,35,70Bit;V-by-OneⓇ HS 24,32,39Bit等的产品,可根据必要的总线宽幅和同期时钟的周波数来选择产品。

LVDS SerDes产品

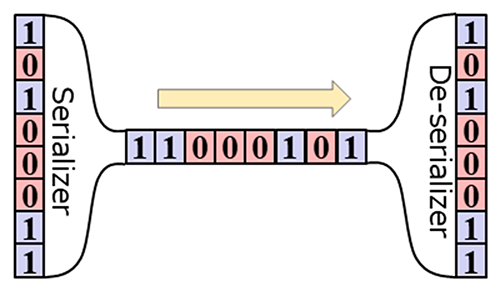

使用LVDS物理层的SerDes会将输入的总线信号以7Bit为单位分割成7倍串联信号,然后通过多根lane来进行数据传送。

在LVDS SerDes中,将并联总线的数据与同期后的时钟信号一起输入Serializer,就会自动转换成以7Bit为单位并进行并联/串联的转换,最后从LVDS的物理层再输出。

DE-Serializer上则会进行相反的过程,复原成总线数据与时钟数据后再输出。(图4)

LVDS SerDes有在LCD面板上使用的FPD-Link与通用数据总线及摄影摄像相关上使用Channel-Link这两种规格。通常这是不同的产品,但THine Electronics的LVDS SerDes产品可通过外部pin(R/F)的设定,同时支持这两种不同的模式。此外,还可以提供通过变更差动驱动器的稳定电流值的设定来达到降低消耗电力和不必要辐射噪音的产品;以及1.8V电源的Low Power Serializer和能使线缆延长及信号分配更容易的Repeater产品等。(请参考表1)

在LVDS SerDes中,将并联总线的数据与同期后的时钟信号一起输入Serializer,就会自动转换成以7Bit为单位并进行并联/串联的转换,最后从LVDS的物理层再输出。

DE-Serializer上则会进行相反的过程,复原成总线数据与时钟数据后再输出。(图4)

图4 LVDS SerDes基本规格

LVDS SerDes有在LCD面板上使用的FPD-Link与通用数据总线及摄影摄像相关上使用Channel-Link这两种规格。通常这是不同的产品,但THine Electronics的LVDS SerDes产品可通过外部pin(R/F)的设定,同时支持这两种不同的模式。此外,还可以提供通过变更差动驱动器的稳定电流值的设定来达到降低消耗电力和不必要辐射噪音的产品;以及1.8V电源的Low Power Serializer和能使线缆延长及信号分配更容易的Repeater产品等。(请参考表1)

表1 THine LVDS & V-by-OneⓇ HS SerDes Family产品案例

CML SerDes产品

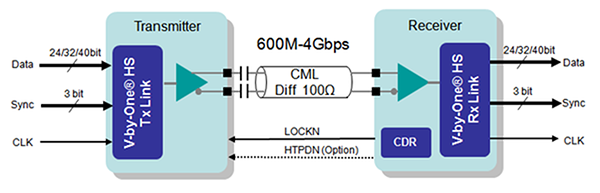

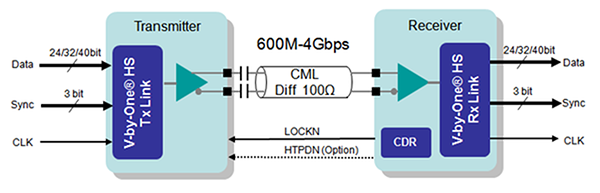

采用CML物理层的V-by-OneⓇ HS SerDes 系列(图5)继承了LVDS SerDes的这些优点,同样实现了串联I/F的高速化与远距离传送。

V-by-OneⓇ HS除与LVDS SerDes同样好用以外,因具有高速性・低延迟・最小的开销等优势,正逐渐成为4K电视 LCD面板的标准I/F;且与LVDS SerDes的Channel Link一样在总线信号的串联传送上也可使用。(请参考V-by-OneⓇ HS在数据通信上的活用 这一技术白皮书)

此外在V-by-OneⓇ HS还能通过将使用8B10B调节后时钟信息编入数据中来解决LVDS SerDes的弱点的LVDS数据与时钟之间的偏离问题。

这一数据与时钟的lane间偏离的改善,并不仅仅是理论上的,而是能应用到高速化和远距离化上的。

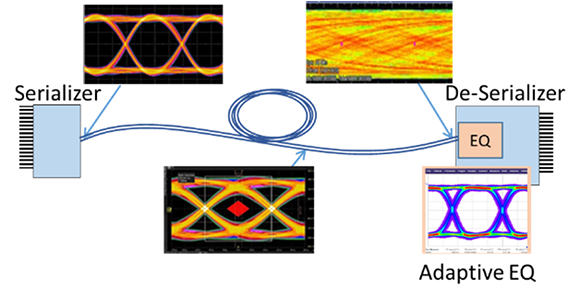

此外像图6这样内置于De-Serializer的自适应均衡器,可不通过手动设定,自动对线缆等传送回路产生的嵌入损失进行补偿。

我们有CML I/F最大可达4Gbps、并联总线I/Fは最大达到32bit(10bitRGB)的LVCMOS、以及39bit(12bit RGB)的LVDS I/F、MIPI CSI-2 I/F等各种产品。(请参考表1)

V-by-OneⓇ HS除与LVDS SerDes同样好用以外,因具有高速性・低延迟・最小的开销等优势,正逐渐成为4K电视 LCD面板的标准I/F;且与LVDS SerDes的Channel Link一样在总线信号的串联传送上也可使用。(请参考V-by-OneⓇ HS在数据通信上的活用 这一技术白皮书)

图5 采用CML物理层的V-by-OneⓇ HS

此外在V-by-OneⓇ HS还能通过将使用8B10B调节后时钟信息编入数据中来解决LVDS SerDes的弱点的LVDS数据与时钟之间的偏离问题。

这一数据与时钟的lane间偏离的改善,并不仅仅是理论上的,而是能应用到高速化和远距离化上的。

图6 RX自适应均衡器

此外像图6这样内置于De-Serializer的自适应均衡器,可不通过手动设定,自动对线缆等传送回路产生的嵌入损失进行补偿。

我们有CML I/F最大可达4Gbps、并联总线I/Fは最大达到32bit(10bitRGB)的LVCMOS、以及39bit(12bit RGB)的LVDS I/F、MIPI CSI-2 I/F等各种产品。(请参考表1)